# Study of the effect of the gate's length on the electrical quality of AlGaN/GaN heterostructures based HEMTs

M. Mostefaoui <sup>a,\*</sup>, A. H. Kacha <sup>b</sup>, A. Rabehi <sup>c</sup>, K. Ameur <sup>b</sup>, H. Mazari <sup>b</sup>, J. M. Bluet <sup>d</sup>

This study examines the influence of gate length variation on the electrical properties of AlGaN/GaN High Electron Mobility Transistors (HEMTs), with a focus on Schottky gate characteristics. Devices with gate lengths of 1  $\mu m$ , 20  $\mu m$ , 30  $\mu m$ , and 100  $\mu m$  were analyzed using I-V measurements to extract key electrical parameters, including series resistance, ideality factor, Schottky barrier height, and leakage current. The results reveal that shorter gate lengths, particularly 1  $\mu m$ , exhibit a high ideality factor (n = 7.51) and substantial series resistance (Rs  $\approx 1.15\times10^9~\Omega$ ), indicating dominant trap-assisted tunneling and recombination effects. In contrast, the 100  $\mu m$  device demonstrates superior performance, with a lower ideality factor (n = 1.12) and reduced leakage current. The Schottky barrier height varies from 0.640 eV (30  $\mu m$ ) to 0.743 eV (100  $\mu m$ ), while leakage current increases significantly in shorter gate devices, reaching 5.50×10<sup>-10</sup> A at 1  $\mu m$ . These findings highlight the crucial role of gate length optimization in improving the performance of GaN-based HEMTs for high-frequency and high-power applications, contributing to the development of next-generation GaN transistors with enhanced efficiency and reliability.

(Received March 28, 2025; Accepted August 7, 2025)

Keywords: HEMT, AlGaN, GaN, Schottky contact, Characterization

#### 1. Introduction

High-electron-mobility transistors (HEMTs) based on AlGaN/GaN heterostructures have attracted significant attention due to their exceptional electrical and thermal properties[1]. These transistors exhibit a wide bandgap, high thermal stability, high breakdown voltage, and superior saturation velocity, making them highly suitable for demanding applications such as radio frequency (RF) communications, high-temperature environments, high-voltage operations, and power electronics[2] [3]. Additionally, their excellent thermal conductivity enhances heat dissipation, further improving their reliability and efficiency. A key feature of GaN-based HEMTs is the presence of a two-dimensional electron gas (2DEG) at the AlGaN/GaN heterointerface. This high-mobility electron channel is formed due to spontaneous and piezoelectric polarization effects within the AlGaN layer, enabling a high carrier density without intentional doping [4]. The combination of high electron mobility and low specific on-resistance gives these devices a significant advantage over conventional field-effect transistors (FETs) in high-power and high-frequency applications [5].

<sup>&</sup>lt;sup>a</sup> Department of Preparatory Classes, Higher School of Saharan Agriculture, Adrar 01000, Algeria

<sup>&</sup>lt;sup>b</sup> Applied Microelectronics Laboratory, Department of Electronics, Djillali Liabes University, BP89, Sidi Bel Abbes 22000, Algeria

<sup>&</sup>lt;sup>c</sup> Telecommunications and Smart Systems Laboratory, University of Djelfa, PO Box 3117, 17000, Djelfa, Algeria

<sup>&</sup>lt;sup>d</sup> Université de Lyon, Institut des Nanotechnologies de Lyon INL-UMR5270, CNRS, INSA de Lyon, Villeurbanne F-69621, France

<sup>\*</sup> Corresponding author: mohamedmicro82@gmail.com https://doi.org/10.15251/JOR.2025.214.495

Despite their remarkable advantages, GaN-based HEMTs still face considerable challenges. These devices are commonly grown on foreign substrates such as silicon (Si), silicon carbide (SiC), or sapphire (Al<sub>2</sub>O<sub>3</sub>), which introduce lattice mismatches that result in high defect densities and dislocations within the epitaxial layers [6] [7]. These defects and interface traps can lead to various performance degradation phenomena, including the kink effect, current collapse, hysteresis, and threshold voltage shifts [8].

A crucial factor in optimizing the electrical performance of AlGaN/GaN HEMTs is the quality of both ohmic and Schottky contacts [9] . The gate contact, which typically forms a Schottky junction with the AlGaN barrier, plays a vital role in determining the device's behavior [10]. Achieving high-performance Schottky contacts requires optimizing key parameters such as the Schottky barrier height (SBH), leakage current suppression, and thermal stability [11] . A higher SBH effectively reduces leakage currents and enhances the breakdown voltage, leading to improved noise performance and power efficiency in HEMTs [12]. The gate length ( $L_g$ ) also significantly influences the electrical performance of these devices. Variations in  $L_g$  impact key parameters such as series resistance ( $R_s$ ), ideality factor (n), and Schottky barrier height ( $\phi_b$ ). A shorter gate length increases the electric field intensity, reducing channel resistance but enhancing parasitic effects, whereas a longer gate length can lead to higher series resistance and slower electron transport[13].

Additionally, gate length variations affect the ideality factor by altering tunneling effects and trap-assisted conduction mechanisms, with shorter gates increasing leakage currents and degrading Schottky contact behavior [14]. The Schottky barrier height is also sensitive to  $L_g$ , as a shorter gate length can enhance quantum mechanical tunneling and lower  $\phi_b$ , leading to higher gate leakage currents, while a longer gate provides a more stable barrier, reducing leakage and improving reliability [15].

This study investigates the impact of gate length variation on the electrical characteristics of AlGaN/GaN HEMTs. By analyzing Schottky gate performance across different gate dimensions, we aim to provide insights into how structural modifications influence key electrical parameters, such as series resistance, ideality factor, and barrier height. This study contributes to the ongoing efforts to optimize GaN-based HEMT technology for high-performance electronic applications.

# 2. Device structure specification

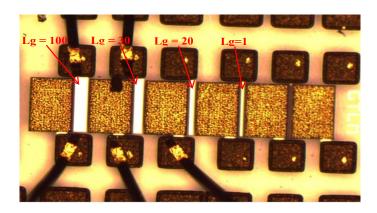

The investigated HEMT structures are based on the  $Al_{0.24}Ga_{0.76}N/GaN$  heterojunction, fabricated with varying gate lengths ( $L_g$ ) of 1  $\mu$ m, 20  $\mu$ m, 30  $\mu$ m, and 100  $\mu$ m, as illustrated in Figure 1. These structures follow a standard design used in high-performance GaN-based transistors.

The epitaxial layers were grown using Low-Pressure Metal-Organic Chemical Vapor Deposition (LP-MOCVD) on a SiC substrate. Growth initiation involved a nucleation layer, followed by an unintentionally doped GaN buffer layer with a thickness of 1.7 µm, which ensures optimal electron transport and structural integrity. The ohmic contacts were fabricated using a multilayer metal stack consisting of titanium (12 nm), aluminum (200 nm), nickel (40 nm), and gold (100 nm), deposited via electron-beam evaporation and annealed at 900°C for 30 seconds under a nitrogen atmosphere to optimize contact resistance. Component isolation was achieved through helium ion implantation, followed by annealing under a nitrogen environment to mitigate implant-induced damage.

Fig. 1. An optical micrograph showing a full view of AlGaN/GaN HEMT structures with varying gate lengths. The outer white region corresponds to the gate length.

The Schottky gate contacts consist of a bilayer structure of molybdenum (40 nm) and gold (300 nm), deposited using electron-beam evaporation. To enhance the device's electrical stability and reduce gate leakage, a passivation layer composed of a 100 nm  $SiO_2$  dielectric layer followed by a 50 nm  $Si_3N_4$  layer was deposited.

The buffer layer serves as a foundational substrate for the upper layers, ensuring structural robustness. An  $Al_{0.28}Ga_{0.72}N$  barrier layer with a well-defined thickness was deposited, remaining unintentionally doped to maintain high electron mobility.

| Table 1. Summarizes t | he key teo | chnological | characteristics of | r ti | he studied structures. |

|-----------------------|------------|-------------|--------------------|------|------------------------|

|                       |            |             |                    |      |                        |

|                             | Al <sub>0.24</sub> Ga <sub>0.72</sub> N |

|-----------------------------|-----------------------------------------|

| Aluminum Molar Fraction (x) | $x_{Al} = 0.24$                         |

| Gate Length (Lg) (µm)       | 1 ,2 ,30 ,100                           |

| Gate Width (Wg) (µm)        | 125                                     |

| Passivation                 | SiO <sub>2</sub> /SiN                   |

| AlGaN Thickness (nm)        | 22                                      |

| GaN Thickness (µm)          | 1.7                                     |

| Substrate                   | SiC                                     |

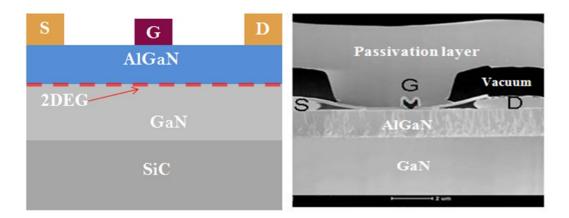

Figure 2 provides the architecture of the studied HEMT structures, displaying the variations in gate lengths. Additionally, a scanning electron microscope (SEM) image showcases the detailed architecture of the fabricated devices.

Current-voltage (I-V) characterization of the fabricated transistors was conducted at room temperature using an HP4155B semiconductor parameter analyzer to evaluate the electrical performance under varying gate lengths. This characterization provides insight into the impact of gate length variation on key transistor parameters, aiding in the optimization of GaN-based HEMT structures for high-frequency and power applications.

Fig. 2. (a) Architecture of the studied HEMT structure; (b) Electron microscope image of a HEMT transistor.

#### 3. Results and discussion

The analysis of the Schottky current in High Electron Mobility Transistors (HEMTs) is essential for understanding the physical mechanisms that govern device performance. Limitations in performance are typically attributed to intrinsic material defects or technological constraints during fabrication. Therefore, evaluating the gate current characteristics, specifically the  $I_g(V_{gs})$  response, provides valuable insight into the quality and reliability of the Schottky gate contact. In a diode configuration, the gate-source voltage  $(V_{gs})$  is applied under both forward  $(V_{gs}>0\ V)$  and reverse  $(V_{gs}<0\ V)$  bias conditions to investigate the behavior of the Schottky junction. In AlGaN/GaN HEMTs, the gate contact forms a Schottky barrier with the AlGaN layer, significantly influencing the gate current and overall transistor performance.

#### 3.1. Gate current analysis as a function of gate length

A widely employed method for extracting key parameters of Schottky diodes is the semi-logarithmic (LnI–V) representation, which provides insight into critical characteristics such as the ideality factor (n), barrier height ( $\phi_b$ ), series resistance ( $R_s$ ), and saturation current ( $I_s$ ). The conduction mechanism in Schottky diodes is primarily governed by the thermionic emission model, which describes current transport across the barrier. The diode current is expressed as:

$$I_{gs} = I_{s} \left[ exp \left( q \frac{V_{gs} - R_{s} I_{gs}}{nkT} \right) - 1 \right]$$

(1)

where  $R_S$  is the series resistance of the diode in forward mode, n is the ideality factor, k is Boltzmann's constant, T is the temperature, q is the elementary charge, and Is the saturation current. When the gate bias is such that thermionic emission dominates, the reverse current  $(I_S)$  remains negligible compared to the exponential component of the forward current. In this region, the voltage drop due to series resistance  $(R_S \times I_{gs})$  is also negligible compared to  $V_{gs}$ , leading to the simplified equation:

$$I_{gs} = I_s \exp\left(\frac{qV_{gs}}{nkT}\right) \tag{2}$$

The Schottky barrier height  $(\phi_b)$  can be extracted from the saturation current using the equation [15]:

$$\phi_{b} = \frac{kT}{q} \ln \left( \frac{SA^{*}T^{2}}{I_{S}} \right) \tag{3}$$

where A\* is the effective Richardson constant, which characterizes electron emission over a potential barrier and is defined as:

$$A^* = \frac{4\pi q m^* k^2}{h^3} \tag{4}$$

where h is Planck's constant and m\* is the effective electron mass in the semiconductor.

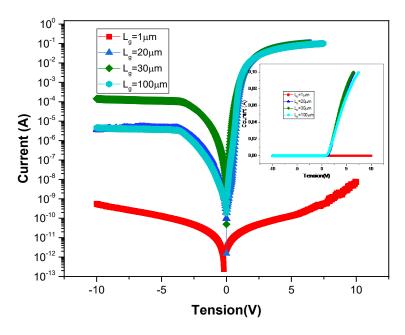

Fig. 3. Experimental forward and reverse bias I-V characteristics of (Mo/Au)-AlGaN/GaN HEMTs, plotted on a logarithmic scale with varying gate lengths (semi-log representation).

Figure 3 presents the experimental gate current ( $I_{gs}$ ) as a function of gate voltage ( $V_{gs}$ ) on a logarithmic scale for different gate lengths ( $L_g=1~\mu m,~20~\mu m,~30~\mu m,$  and  $100~\mu m$ ). Measurements were performed under forward bias (0 V to 10 V) and reverse bias (down to -10 V) at room temperature in a dark environment.

To investigate the conduction mechanisms in the studied Schottky Barrier Diode (SBD), key electrical parameters such as the ideality factor (n), saturation current ( $I_S$ ), barrier height ( $\varphi_b$ ), and series resistance ( $R_S$ ) were extracted from the forward bias I-V characteristics. The results are summarized in Table 2.

| 7 | Table 2. Presents th | e extracted | d Electrical parai | neters obtained f | rom $ln(I_{gs})$ - $V_{gs}$ |  |

|---|----------------------|-------------|--------------------|-------------------|-----------------------------|--|

|   | C + I +1 (I )        | T           | T [A]              | D [O]             |                             |  |

| Gate Length (Lg) | n    | Is [A]                   | $R_{s}\left[\Omega\right]$ | φ <sub>b</sub> [eV] |

|------------------|------|--------------------------|----------------------------|---------------------|

| 1 μm             | 7.51 | 2.3389×10 <sup>-12</sup> | $1.15 \times 10^9$         | 0.725               |

| 20 μm            | 1.62 | 6.566×10 <sup>-11</sup>  | 88.89                      | 0.716               |

| 30 μm            | 1.27 | 1.8618×10 <sup>-9</sup>  | 94.46                      | 0.640               |

| 100 μm           | 1.12 | 1.17×10 <sup>-10</sup>   | 112.62                     | 0.743               |

The I-V characteristics exhibit a linear variation in the range 0 V <  $V_{gs}$  < 1.5 V. Beyond 1.6 V, the influence of series resistance (R<sub>S</sub>) becomes dominant. Notably, at  $L_g$  = 1  $\mu$ m, Rs reaches an exceptionally high value of 1.15×10<sup>9</sup>  $\Omega$ , whereas for  $L_g$  = 100  $\mu$ m, R<sub>S</sub> decreases to 112.62  $\Omega$ , demonstrating a substantial reduction in resistance with increasing gate length.

The ideality factor (n) also exhibits a decreasing trend with increasing  $L_g$ , transitioning from 7.51 at  $L_g = 1~\mu m$  to 1.12 at  $L_g = 100~\mu m$ . A high ideality factor indicates the presence of additional conduction mechanisms such as trap-assisted tunneling or recombination currents, which are prevalent in short-gate structures. In contrast, for larger gate lengths, the dominant transport mechanism shifts to thermionic emission.

The barrier height ( $\phi_b$ ) shows a moderate increase from 0.725 eV ( $L_g = 1 \mu m$ ) to 0.743 eV ( $L_g = 100 \mu m$ ), suggesting an improvement in gate contact quality with increasing gate length.

Gate length ( $L_g$ ) significantly impacts the saturation current ( $I_s$ ) in AlGaN/GaN HEMTs. At short gate lengths (1 µm), Is is minimal (2.3389×10<sup>-12</sup>A) due to strong gate control and a high Schottky barrier height ( $\phi_b = 0.725 eV$ ), reducing leakage current. For intermediate lengths (20–30 µm),  $I_s$  increases sharply (1.8618×10<sup>-9</sup> µm) as the barrier height decreases, enhancing carrier injection. At long gate lengths (100 µm),  $I_s$  decreases slightly (1.17×10<sup>-10</sup>A), likely due to charge trapping and increased series resistance.

## 3.2. Junction resistance and rectifying behavior

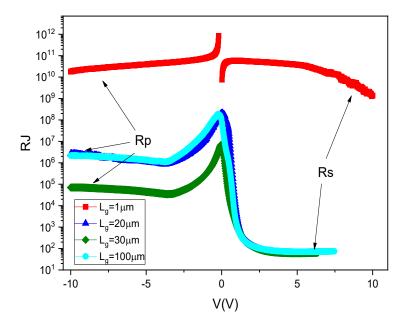

The series resistance ( $R_S$ ) and shunt resistance ( $R_P$ ) are critical parameters that significantly influence the performance and reliability of Schottky diodes. These values are extracted from the junction resistance ( $R_j$ ) versus applied bias voltage (V) plot. The junction resistance ( $R_j$ ) was computed using Ohm's Law, and is depicted in Fig.4[16]:

$$R_J = \frac{V_{gs}}{I_{gs}}$$

To further assess the impact of gate length on device performance, the variations in  $R_S$  and  $R_P$  were analyzed across different gate dimensions. These parameters play a crucial role in determining the overall rectification efficiency and leakage characteristics of the device.

A low RS indicates a higher current flow across the junction, while an  $R_P$  value approaching infinity suggests minimal leakage current. In the junction resistance plot (Fig. 4), the lower region in the forward bias section provides the  $R_S$  value, whereas the peak resistance observed in the reverse bias section corresponds to  $R_P[16]$ .

Fig. 4. Junction resistance plots with varying gate lengths.

| Gate Length (Lg)        | Rs                  | $R_P$                |

|-------------------------|---------------------|----------------------|

| $L_g = 1 \mu m$         | 3.3×10 <sup>9</sup> | 2.5×10 <sup>10</sup> |

| $L_g = 20 \mu m$        | 71.3                | 4×10 <sup>6</sup>    |

| $L_g = 30 \mu m$        | 71.3                | 2.5×10 <sup>6</sup>  |

| I <sub>-</sub> = 100 µm | 71.3                | $7.2 \times 10^4$    |

Table 4. Presents the extracted  $R_S$  and  $R_P$  values for different gate lengths  $(L_g)$ .

The results indicate that for shorter gate lengths ( $L_g=1\mu m$ ),  $R_S$  is significantly higher, leading to increased resistance at the junction. However, for larger gate lengths ( $L_g \ge 20\mu m$ ),  $R_S$  stabilizes at approximately 71.3  $\Omega$ . Meanwhile,  $R_P$  decreases as the gate length increases, suggesting a higher leakage current for longer gate devices (Table 4).

These findings highlight the impact of gate length on diode performance, with shorter gate lengths exhibiting higher resistance but lower leakage, while longer gate lengths provide better current flow but increased leakage.

The results confirm that at shorter gate lengths, the junction exhibits significantly higher resistance, likely due to increased leakage currents. To validate this hypothesis, the rectifying ratio (RR) was calculated as the ratio between the forward and reverse currents[17]:

$$RR = \frac{I_{Forward}}{I_{Reverse}}$$

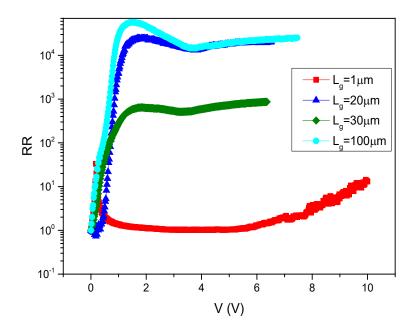

The rectification ratio (RR) of the (Mo/Au)-AlGaN/GaN structures varies with gate length, highlighting its impact on device performance. RR curves are presented in Fig.5.

The rectification ratio (RR) of the studied photodiode structures was calculated in the dark at a temperature of 300 K. The RR is a crucial parameter for evaluating the electrical characteristics and performance of diodes[18], as it indicates their ability to efficiently rectify current. A higher RR value typically signifies better diode performance with reduced leakage currents and stronger Schottky behavior. These measurements provide insight into the structural and material properties influencing the device's operation, particularly under varying environmental conditions.

Fig. 5. The rectifying ratio curves with varying gate lengths.

The RR values are 15 for  $L_g=1\mu m$ ,  $1x10^4$  for  $L_g=20\mu m$ ,  $1x10^3$  for  $L_g=30$   $\mu m$ , and  $2x10^4$  for  $L_g=100\mu m$ . These results indicate that longer gate lengths exhibit higher rectification ratios, confirming their superior Schottky behavior. Conversely, shorter gate devices suffer from increased leakage currents, leading to poor rectification performance. This trend underscores the critical role of gate length in determining the diode's electrical characteristics.

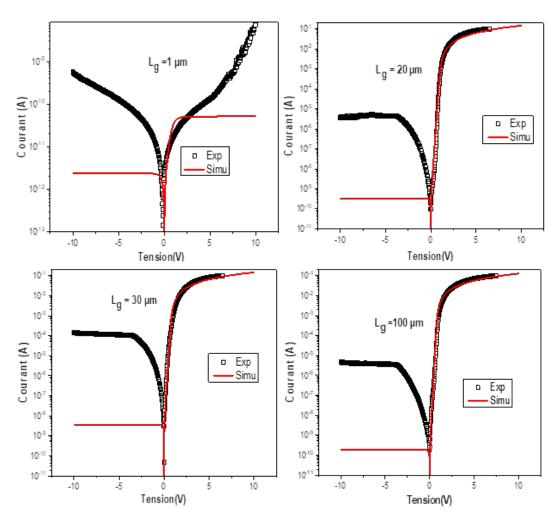

## 3.3. Estimation of leakage current

To quantitatively evaluate the leakage current, the experimental  $I_g(V_{gs})$  curves were compared with simulated data obtained by solving the thermionic emission equation (Equation 1) using the extracted electrical parameters listed in Table 2. Figure 6 presents a comparison between the experimental and simulated I-V characteristics for different gate lengths ( $L_g = 1 \mu m$ ,  $L_g = 20 \mu m$ ,  $L_g = 30 \mu m$ , and  $L_g = 100 \mu m$ ).

Fig. 6. Experimental and simulated current–voltage characteristics of the (Mo/Au)–AlGaN/GaN HEMTs with different gate lengths.

A noticeable deviation is observed between the simulated and experimental I-V characteristics for the sample with  $L_{\rm g}=1~\mu m$ , indicating that the thermionic emission mechanism is not the dominant transport process in this structure. Instead, additional conduction mechanisms, such as tunneling effects and recombination currents in forward bias, as well as leakage currents in reverse bias, significantly contribute to the gate current.

For devices with larger gate lengths, the simulated and experimental curves exhibit excellent agreement under forward bias, suggesting that thermionic emission predominates in

these structures. However, under reverse bias, the experimental current exceeds the simulated values for all gate lengths, indicating the presence of leakage currents that are not accounted for by the thermionic model.

To quantify the leakage contribution, the leakage current was estimated by computing the difference between the experimental and simulated reverse current. The extracted values are summarized in Table 3.

| Gate Length (Lg)    | Leakage Current (Ig)   |

|---------------------|------------------------|

| $L_g = 1 \mu m$     | 5.50×10 <sup>-10</sup> |

| $L_g = 20 \mu m$    | 4.13×10 <sup>-6</sup>  |

| $L_g = 30 \ \mu m$  | 1.13×10 <sup>-4</sup>  |

| $L_g = 100 \ \mu m$ | 3.46×10 <sup>-6</sup>  |

Table 4. Presents the reverse current as a function of the gate length  $(L_g)$ .

Table 3 illustrates the evolution of leakage current with gate length ( $L_g$ ). Although the leakage current is relatively low for  $L_g = 1~\mu m$  (5.5 × 10<sup>-10</sup> A), it remains significant due to the inherently low gate current in this structure (< 10<sup>-9</sup> A). For devices with longer gate lengths, the leakage current is negligible compared to the total gate current, confirming that thermionic emission is the dominant conduction mechanism in these structures.

#### 4. Conclusion

This study systematically analyzed the impact of gate length variation on the electrical performance of AlGaN/GaN HEMTs, focusing on Schottky gate characteristics and key device parameters. The results show that shorter gate lengths lead to higher series resistance and ideality factors, indicating dominant trap-assisted tunneling and recombination effects. In contrast, longer gate lengths improve gate contact quality, reduce parasitic effects, and enhance thermionic emission behavior. Leakage current analysis further reveals that short-gate devices suffer from significant leakage due to enhanced electric fields and defect-assisted conduction, whereas longer gate devices exhibit lower leakage and better rectification performance. These findings highlight the importance of gate length optimization in achieving a balance between minimizing leakage currents and maximizing efficiency. This work provides valuable insights for advancing GaN-based HEMT fabrication, paving the way for more reliable and efficient high-frequency, high-power, and RF applications.

#### References

[1] B. Kim, S. Park, S.R. Hall, Materials, 17(22), 5515 (2024); https://doi.org/10.3390/ma17225515

[2] A. Akshaykranth, J. Ajayan, S. Bhattacharya, D. Nirmal, S, Results Eng. 25, 104151, (2025); https://doi.org/10.1016/j.rineng.2025.104151

[3] M. Pilati, M. Buffolo, F. Rampazzo, B. Lambert, D. Sommer, J. Grünenpütt, C. De Santi, G. Meneghesso, E. Zanoni, M. Meneghini, Microelectron. Reliab. 150,1-5, (2023); <a href="https://doi.org/10.1016/j.microrel.2023.115131">https://doi.org/10.1016/j.microrel.2023.115131</a>

[4] S. Milazzo, G. Greco, S. Di, P. Fiorenza, F. Giannazzo, C. Bongiorno, L. Gervasi, S. Mirabella, F. Iucolano, F. Roccaforte, Applied Surface Science, 15(679), 161316 (2025);

- https://doi.org/10.1016/j.apsusc.2024.161316

- [5] J. Osvald, T. Lalinský, G. Vanko, Appl. Surf. Sci, 15(461), 206-211(2018); https://doi.org/10.1016/j.apsusc.2018.06.113

- [6] M. Whiteside, S. Arulkumaran, Y. Dikme, A. Sandupatla, G.I. Ng, Materials Science & Engineering B, 262 114707 (2020); https://doi.org/10.1016/j.mseb.2020.114707

- [7] Z. Xi, Y. Wang, X. Fei, B. Sun, H. Huang, Y. Song, F. Cao, Nucl. Eng. Technol. 57, 103538, (2025); <a href="https://doi.org/10.1016/j.net.2025.103538">https://doi.org/10.1016/j.net.2025.103538</a>

- [8] R. Baca-arroyo, e-Prime Advances in Electrical Engineering, 11, 100954 (2025); <a href="https://doi.org/10.1016/j.prime.2025.100954">https://doi.org/10.1016/j.prime.2025.100954</a>

- [9] M. Wzorek, M. Ekielski, E. Brzozowski, A. Taube, Semicond. Process. 153 (2023) 107157; <a href="https://doi.org/10.1016/j.mssp.2022.107157">https://doi.org/10.1016/j.mssp.2022.107157</a>

- [10] C. Tang, G. Xie, K. Sheng, Microelectronics Reliability, 2 (55), 347-351, (2015); <a href="https://doi.org/10.1016/j.microrel.2014.10.018">https://doi.org/10.1016/j.microrel.2014.10.018</a>

- [11] C. Sharma, A.K. Visvkarma, R. Laishram, A. Kumar, D.S. Rawal, S. Vinayak, R. Singh, Microelectronics Reliability 105, 113565, (2020); <a href="https://doi.org/10.1016/j.microrel.2019.113565">https://doi.org/10.1016/j.microrel.2019.113565</a>

- [12] S. Chakraborty, T. Kim, Transistors 13(1), 84 (2022); https://doi.org/10.3390/mi13010084

- [13] U.K. Mishra, P. Parikh, Y. Wu, Proceedings of the IEEE, 6 (90), 1022 1031, (2002); <a href="https://doi.org/10.1109/JPROC.2002.1021567">https://doi.org/10.1109/JPROC.2002.1021567</a>

- [14] J. Pruefer, J. Leise, G. Darbandy, A. Nikolaou, H. Klauk, J.W. Borchert, B. Iñíguez, T. Gneiting, A. Kloes, S. Member, Compact Modeling of Short-Channel Effects in Staggered Organic Thin-Film Transistors, 67, 5082-5090, (2020); https://doi.org/10.1109/TED.2020.3021368

- [15] R. Vetury, N.Q. Zhang, S. Keller, U.K. Mishra, IEEE Transactions on Electron Devices, 11(67), 560-566, (2001); <a href="https://doi.org/10.1109/16.906451">https://doi.org/10.1109/16.906451</a>

- [16] V.R. Reddy, C.V. Prasad, V. Janardhanam, C.J. Choi, Journal of Materials Science: Materials, 32 ,8092-8105, (2021); <a href="https://doi.org/10.1007/s10854-021-05532-2">https://doi.org/10.1007/s10854-021-05532-2</a>

- [17] A.H. Kacha, M.N. Amroun, B. Akkal, Z. Benamara, Semiconductors. 55, S54-S61, (2021); https://doi.org/10.1134/S1063782621090086

- [18] Ş. Karataş, N. Berk, Optical Materials, 126, 112231 (2022); https://doi.org/10.1016/j.optmat.2022.112231